## LCP1521S/LCP152DEE

# ASD (Application Specific Devices)

## Programmable transient voltage suppressor for SLIC protection

### **Features**

- Dual programmable transient suppressor

- Wide negative firing voltage range: V<sub>MGL</sub> = -150 V max.

- Low dynamic switching voltages: V<sub>FP</sub> and V<sub>DGI</sub>

- Low gate triggering current: I<sub>GT</sub> = 5 mA max

- Peak pulse current:  $I_{PP} = 30 \text{ A} (10/1000 \text{ µs})$

- Holding current: I<sub>H</sub> = 150 mA min

- Low space consuming package

## **Description**

These devices have been especially designed to protect new high voltage, as well as classical SLICs, against transient overvoltages.

Positive overvoltages are clamped by 2 diocles. Negative surges are suppressed by 2 thurstors, their breakdown voltage being referenced to -V<sub>BAT</sub> through the gate.

These components present a very low gave triggering current (I<sub>G</sub>.) in order to reduce the current constantion on printed circuit board during the firing phase.

### **Segefits**

TRISILs™ arc r. it subject to ageing and provide a fail safe racde in short circuit for a better level of protection. Trisils are used to ensure equipment maets various standards such as UL60950, ITC950 / CSA C22.2, UL1459 and FCC part 68. Trisils have UL94 V0 approved resin (Trisils are UL497B approved [file: E136224]).

TM: TRISIL is a trademark of STMicroelectronics

### Order codes

| Part Number  | Marking |

|--------------|---------|

| LCP1521S     | CP152S  |

| LCP1521SFL   | CP152S  |

| LCP152.0EERL | LCP152  |

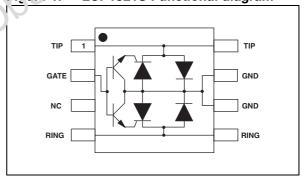

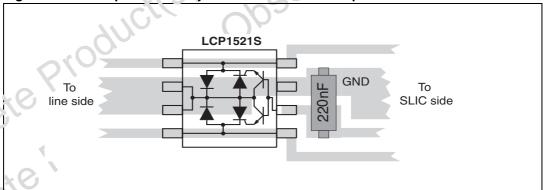

Figure 1. LCP1521S Functional diagram

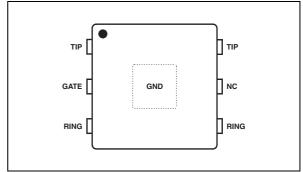

Figure 2. LCP152DEE Functional diagram

#### **Characteristics** 1

Table 1. Standards compliance

|                                        | •                               |                         |                                    | 1                         | ı                                            |

|----------------------------------------|---------------------------------|-------------------------|------------------------------------|---------------------------|----------------------------------------------|

| Standard                               | Peak<br>surge<br>voltage<br>(V) | Voltage<br>waveform     | Required<br>peak<br>current<br>(A) | Current<br>waveform       | Minimum serial resistor to meet standard (Ω) |

| GR-1089 Core First level               | 2500<br>1000                    | 2/10 μs<br>10/1000 μs   | 500<br>100                         | 2/10 μs<br>10/1000 μs     | 12<br>24                                     |

| GR-1089 Core<br>Second level           | 5000                            | 2/10 μs                 | 500                                | 2/10 μs                   | 24                                           |

| GR-1089 Core<br>Intra-building         | 1500                            | 2/10 μs                 | 100                                | 2/10 μs                   | 6                                            |

| ITU-T-K20/K21                          | 6000<br>1500                    | 10/700 μs               | 150<br>37.5                        | 5/310 μς                  | 110<br>0                                     |

| ITU-T-K20 (IEC 61000-4-2)              | 8000<br>15000                   | 1/60 ns                 |                                    | nt discharge<br>discharge | 0                                            |

| VDE0433                                | 4000<br>2000                    | 10/700 μs               | 100<br>50                          | 5/310 µs                  | 60<br>10                                     |

| VDE0878                                | 4000<br>2000                    | 1.2/50 ¦!٤              | 100<br>50                          | 1/20 µs                   | 0<br>0                                       |

| IEC61000-4-5                           | 4000<br>4000                    | າ 770 ) µs<br>1 2/50 µs | 100<br>100                         | 5/310 μs<br>8/20 μs       | 60<br>0                                      |

| FCC Part 68,<br>lightning surge type A | 1500<br>800                     | 10/160 μs<br>10/560 μs  | 200<br>100                         | 10/160 μs<br>10/560 μs    | 22.5<br>15                                   |

| FCC Part 68, lightning surge type B    | 1000                            | 9/720 µs                | 25                                 | 5/320 µs                  | 0                                            |

| li       | ightning sur             | ge type A         | 800     | 10/560  | us   | 100 | 10/5 | 60 µs |     | 15    |

|----------|--------------------------|-------------------|---------|---------|------|-----|------|-------|-----|-------|

|          | FCC Part 68 ightning sur |                   | 1000    | 9/720 µ | IS   | 25  | 5/32 | 20 µs |     | 0     |

| <u>T</u> | able 2.                  | กษะกลl resi       | stances |         |      |     |      |       |     |       |

|          | Symco!                   | , ,               | S Par   | ameter  |      |     |      | Va    | lue | Unit  |

|          | 8                        | Junction to ambie | ant     |         | SO-8 |     |      | 1     | 20  | ° C/W |

| 76       | r³τn(j-a)                | diretion to amble | 21 IL   |         | QFN  |     |      | 1     | 40  | 0/11  |

| 0/250,   | ie P'                    | O                 |         |         |      |     |      |       |     |       |

| Obsole   |                          |                   |         |         |      |     |      |       |     |       |

LCP1521S/LCP152DEE Characteristics

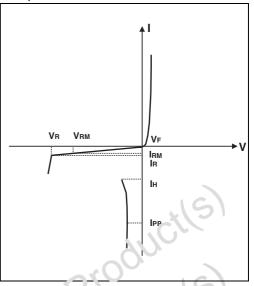

Electrical characteristics ( $T_{amb} = 25^{\circ} C$ ) Table 3.

| Symbol           | Parameter                             |

|------------------|---------------------------------------|

| I <sub>GT</sub>  | Gate triggering current               |

| I <sub>H</sub>   | Holding current                       |

| I <sub>RM</sub>  | Reverse leakage current LINE / GND    |

| I <sub>RG</sub>  | Reverse leakage current GATE / LINE   |

| V <sub>RM</sub>  | Reverse voltage LINE / GND            |

| V <sub>GT</sub>  | Gate triggering voltage               |

| V <sub>F</sub>   | Forward drop voltage LINE / GND       |

| V <sub>FP</sub>  | Peak forward voltage LINE / GND       |

| V <sub>DGL</sub> | Dynamic switching voltage GATE / LINE |

| V <sub>RG</sub>  | Reverse voltage GATE / LINE           |

| С                | Capacitance LINE / GND                |

Absolute ratings (T<sub>amb</sub> = 25° C, unless otherwise specified) Table 4.

| Sym             | nbol             |                                                | Parameter           | loite d                | Value       | Unit |

|-----------------|------------------|------------------------------------------------|---------------------|------------------------|-------------|------|

|                 |                  |                                                | 100                 | 10/1000 μs<br>8/20 μs  | 30<br>100   |      |

|                 |                  |                                                | Ub.                 | 10/560 μs              | 35          |      |

| I <sub>Pl</sub> | o <sub>P</sub> P | eak pulse current                              |                     | 5/310 μs               | 40          | Α    |

|                 |                  |                                                |                     | 10/160 µs              | 50          |      |

|                 |                  | 1/5                                            | , C                 | 1/20 µs                | 100         |      |

|                 |                  | CIL                                            | 003                 | 2/10 µs                | 150         |      |

|                 |                  | lon rong itwo gurae neels                      | on state current    | t = 20 ms              | 18          |      |

| I <sub>TS</sub> |                  | lon repelitive surge peak<br>50 Hz sinusoidal) | on-state current    | t = 200 ms             | 10          | Α    |

|                 |                  | 70 12 Siridoordary                             |                     | t = 1 s                | 7           |      |

| Jas             | SM N             | Maximum gate current (5                        | OHz sinusoidal)     | t = 10 ms              | 2           | Α    |

| V <sub>MI</sub> | ılg N            | /laximum voltage LINE/G                        | ND                  | -40° C < Tamb < +85° C | -150        | V    |

| V <sub>M</sub>  | IGL N            | /laximum voltage GATE/l                        | INE                 | -40° C < Tamb < +85° C | -150        | V    |

| T <sub>s</sub>  | stg S            | Storage temperature rang                       | je                  |                        | -55 to +150 | ° C  |

| Ĭ               |                  | Maximum junction tempe                         | rature              |                        | 150         | ٠.   |

| Ti              | LN               | laximum lead temperatu                         | re for soldering du | uring 10 s.            | 260         | ° C  |

| Table           | le 5.            | Repetitive peak pu                             | lse current         |                        |             |      |

| Sy              | /mbol            | Definition                                     | Example             | % IPP                  |             |      |

|                 |                  |                                                |                     | 100                    |             |      |

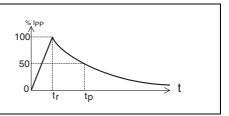

Table 5. Repetitive peak pulse current

| Symbol         | Definition          | Example                                                        |

|----------------|---------------------|----------------------------------------------------------------|

| t <sub>r</sub> | Rise time (µs)      | Pulse waveform                                                 |

| t <sub>p</sub> | Pulse duration (µs) | 10/1000 $\mu$ s:<br>$t_r = 10 \ \mu$ s<br>$t_p = 1000 \ \mu$ s |

Characteristics LCP1521S/LCP152DEE

Table 6. Parameters related to the diode LINE / GND ( $T_{amb} = 25^{\circ} C$ )

| Symbol                         |                                   | Test condition             | าร                                                    | Max          | Unit |

|--------------------------------|-----------------------------------|----------------------------|-------------------------------------------------------|--------------|------|

| V <sub>F</sub>                 | I <sub>F</sub> = 5A               |                            | t = 500 μs                                            | 3            | V    |

| V <sub>FP</sub> <sup>(1)</sup> | 10/700 μs<br>1.2/50 μs<br>2/10 μs | 1.5 kV<br>1.5 kV<br>2.5 kV | $R_S = 10 \Omega$ $R_S = 10 \Omega$ $R_S = 62 \Omega$ | 5<br>9<br>30 | V    |

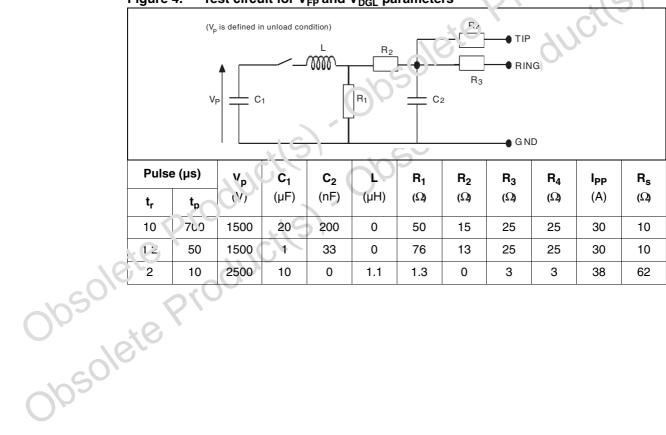

<sup>1.</sup> See test circuit for VFP (Figure 4.): RS is the protection resistor located on the line card.

Table 7. Parameters related to the protection Thyristors ( $T_{amb} = 25^{\circ}$  C, unless otherwise specified)

| Symbol           | Test cond                                            | itions                  |                                                                      | Тур  | Max           | Unit |

|------------------|------------------------------------------------------|-------------------------|----------------------------------------------------------------------|------|---------------|------|

| I <sub>GT</sub>  | V <sub>GND / LINE</sub> = -48 V                      |                         |                                                                      | 0.1  | 5             | n)A  |

| I <sub>H</sub>   | V <sub>GATE</sub> = -48 V <sup>(1)</sup>             |                         |                                                                      | 150  | 10cc          | mA   |

| $V_{GT}$         | at I <sub>GT</sub>                                   |                         |                                                                      |      | 2.5           | V    |

| I <sub>RG</sub>  | V <sub>RG</sub> = -150 V<br>V <sub>RG</sub> = -150 V |                         | Γ <sub>j</sub> = 25° C<br>Γ <sub>j</sub> = 85° C                     | (0)  | 5<br>50       | μА   |

| V <sub>DGL</sub> | 1.2/50 μs 1.5 kV                                     | $R_S = 10 \Omega$ $I_I$ | <sub>PP</sub> = 30 A<br><sub>PP</sub> = 30 A<br><sub>PP</sub> = 38 A | 100) | 7<br>10<br>25 | V    |

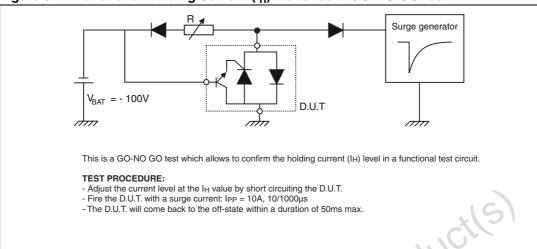

<sup>1.</sup> see functional holding current (I<sub>H</sub>) test circuit

Table 8. Parameter Nelateo to diode and protection Thyristors (Tamb = 25° C, unless otherwise specified)

| Symbol          | Test conditions                                                                                                                           |                                                              | Тур      | Max     | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|---------|------|

| I <sub>Ri</sub> | V <sub>GATE / LINE</sub> = -1 V V <sub>RM</sub> = -150 V<br>VG <sub>ATE / LINE</sub> = -1 V V <sub>RM</sub> = -150 V                      | $T_j = 25^{\circ} \text{ C}$<br>$T_j = 85^{\circ} \text{ C}$ |          | 5<br>50 | μΑ   |

| Ole C           | $V_R = 50 \text{ V bias}, V_{RMS} = 1 \text{ V}, F = 1 \text{ MHz}$<br>$V_R = 2 \text{ V bias}, V_{RMS} = 1 \text{ V}, F = 1 \text{ MHz}$ |                                                              | 15<br>35 |         | pF   |

| Observe Pr      |                                                                                                                                           |                                                              |          |         |      |

| Obsolu          |                                                                                                                                           |                                                              |          |         |      |

4/11

<sup>2.</sup> see test circuit for  $V_{\hbox{\scriptsize DG}}$  The oscillations with a time duration lower than 50ns are not taken into account.

LCP1521S/LCP152DEE Characteristics

Figure 3. Functional Holding Current (I<sub>H</sub>) test circuit: GO-NO GO test

Figure 4. Test circuit for  $V_{FP}$  and  $V_{DGL}$  parameters

## 2 Technical information

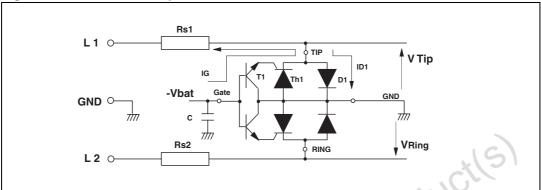

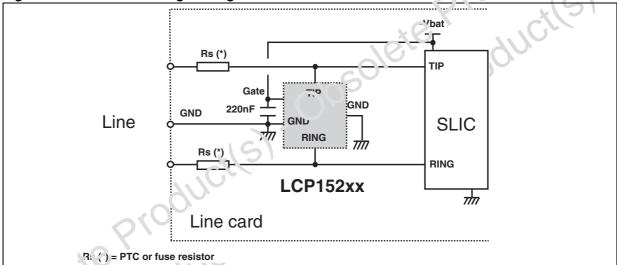

Figure 5. LCP152 concept behavior

Figure 5. shows the classical protection circuit using the LCP152 crowpar concept. This topology has been developed to protect the new high voltage SI ICs. It allows to program the negative firing threshold while the positive clamping value is rived at GND.

When a negative surge occurs on one wire (L1 for example) a current IG flows through the base of the transistor T1 and then injects a current in the gate of the thyristor Th1. Th1 fires and all the surge current flows through the ground. If the surge when the current flowing through Th1 becomes less negative than the holding current IH, then Th1 switches off.

When a positive surge occurs on one wire (£1 for example) the diode D1 conducts and the surge current flows through the ground.

Figure 6. Example of PC5 layout based on LCP152S protection

Figure 6. shows the classical PCB layout used to optimize line protection.

The capacitor C is used to speed up the crowbar structure firing during the fast surge edges.

This allows to minimize the dynamical breakover voltage at the SLIC Tip and Ring inputs during fast strikes. Note that this capacitor is generally present around the SLIC - Vbat pin.

So to be efficient it has to be as close as possible from the LCP152 Gate pin and from the reference ground track (or plan) (see *Figure 6*.). The optimized value for C is 220 nF.

The series resitors Rs1 and Rs2 designed in *Figure 5.* represent the fuse resistors or the PTC which are mandatory to withstand the power contact or the power induction tests

imposed by the various country standards. Taking into account this fact the actual lightning surge current flowing through the LCP is equal to:

$$I_{surge} = V_{surge} / (R_g + R_s)$$

With:

V <sub>surge</sub> = peak surge voltage imposed by the standard.

R<sub>a</sub> = series resistor of the surge generator

R<sub>s</sub> = series resistor of the line card (e.g. PTC)

e.g. For a line card with 30  $\Omega$  of series resistors which has to be qualified under GR1089 Core 1000V 10/1000  $\mu$ s surge, the actual current through the LCP152 is equal to:

$$I_{surge} = 1000 / (10 + 30) = 25 A$$

The LCP152 is particularly optimized for the new telecom applications such as the fiber in the loop, the WLL, the remote central office. In this case, the operating voltages are smaller than in the classical system. This makes the high voltage SLICs particularly such able.

The schematics of Figure 7. give the most frequent topology used for these applications.

Figure 7. Protection of high voltage SLIC

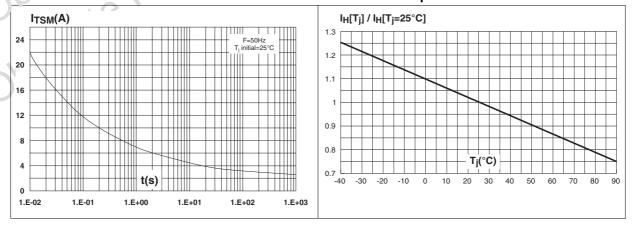

Figure 3. Surge peak current versus overload Figure 9. duration

Relative variation of holding current versus junction temperature

577

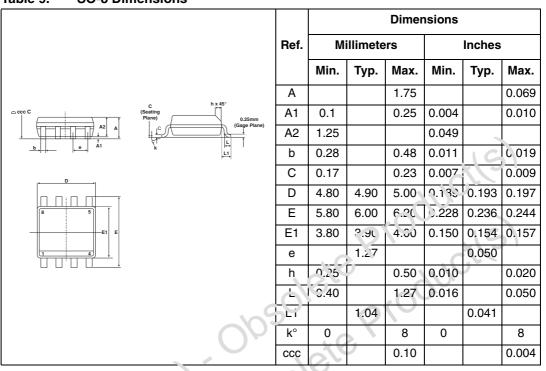

#### **Package information** 3

Table 9. **SO-8 Dimensions**

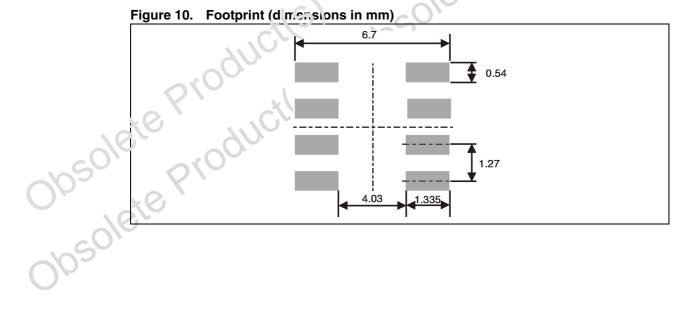

Figure 10. Footprint (dimensions in mm)

577 8/11

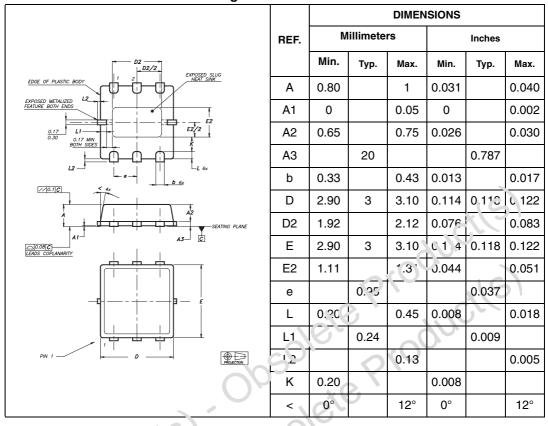

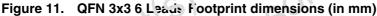

Table 10. QFN 3x3 6 Leads Package dimensions

9/11

#### **Ordering information** 4

| Part Number                | Marking | Package    | Weight  | Base qty | Delivery mode |

|----------------------------|---------|------------|---------|----------|---------------|

| LCP1521S                   | CP152S  | SO-8       | 0.11 g  | 100      | Tube          |

| LCP1521SRL <sup>(1)</sup>  | CP152S  | 30-6       | 0.11 9  | 2500     | Tape and reel |

| LCP152DEERL <sup>(1)</sup> | LCP152  | QFN 3x3 6L | 0.022 g | 3000     | Tape and reel |

<sup>1.</sup> Preferred device

#### **Revision history** 5

| Date        | Revision | Description of C′ ເຂ no es                                                                                                                                                                 |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sep-2003    | 1A       | First issue.                                                                                                                                                                               |

| 08-Dec-2004 | 2        | 1/ Page 2 table 3: Thermal resistances changed from 130° C/W (SO-8) to 120° C/W at a room 170° C/W (QFN) to 140° C/W. 2/ SO-8 and QFN to print dimensions added.                           |

| 17-Feb-2005 | 3        | Table 9 บา วงจะ 4: correction of typo on capacitance unit.                                                                                                                                 |

| 03-May-2005 | 4        | Table 5 c page 3: I <sub>TSM</sub> value @ t= 1s from 4 A to 4.5 A.                                                                                                                        |

| 07-Jul-2006 | 5        | F'eplaced QFN package illustration on page 1. Reformatted dccument to current layout standard. Values of I <sub>TSM</sub> modified in Table 4. SO-8 package dimensions updated in Table 9. |

| ete Prof    |          |                                                                                                                                                                                            |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia rics (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and servings described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property 'ig 't's 's granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warrancy covering the use in any manner whatsoever of such third party products or services or any intellectual property contained the rain.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF CANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VINING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OF WANDANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROFINITY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE VISED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST | roducts with provisions different from the statements and/or technical features set forth in this document shall immediately void any warran'ty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

577